# Basics of SPI: Timing Requirements and Switching Characteristics TI Precision Labs – Digital Communications

Presented by Alex Smith Prepared by Joseph Wu

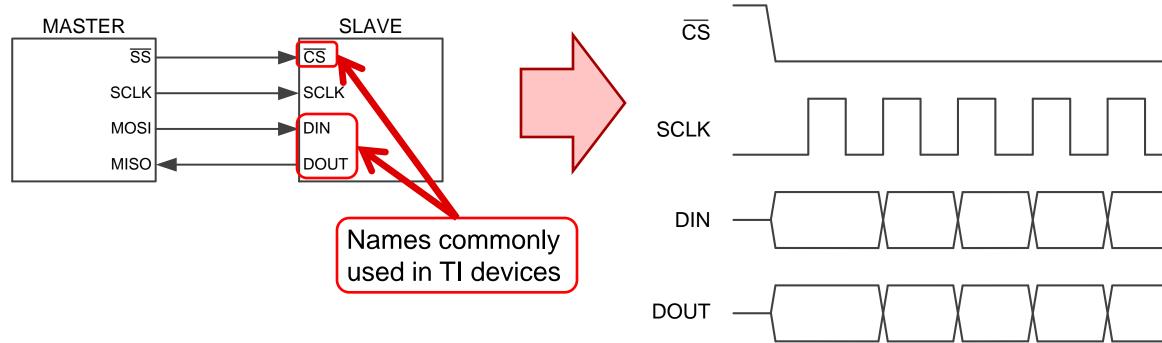

# **SPI Communication**

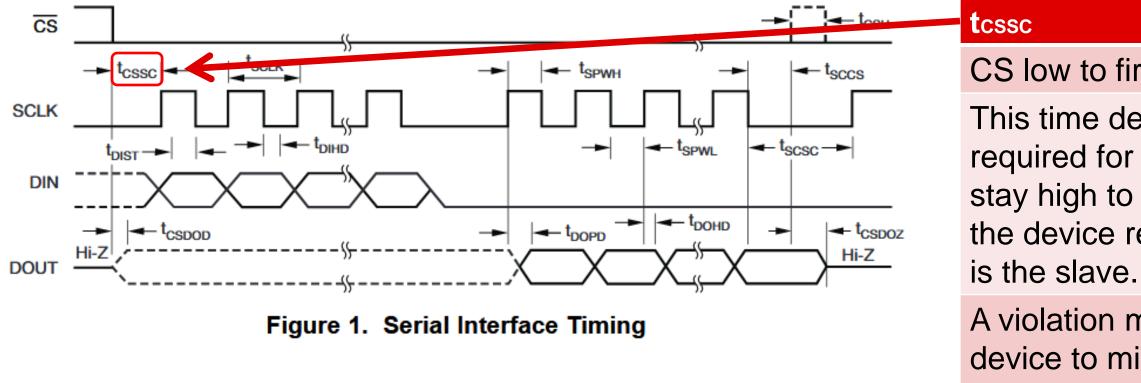

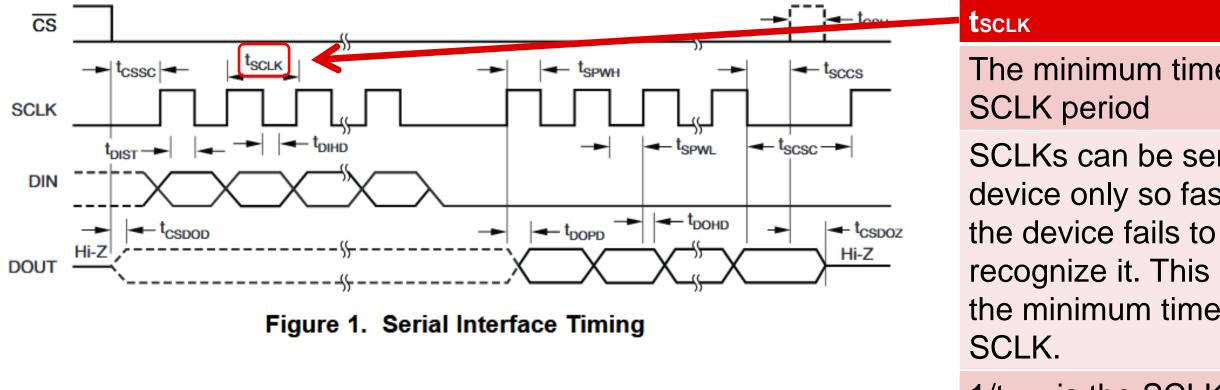

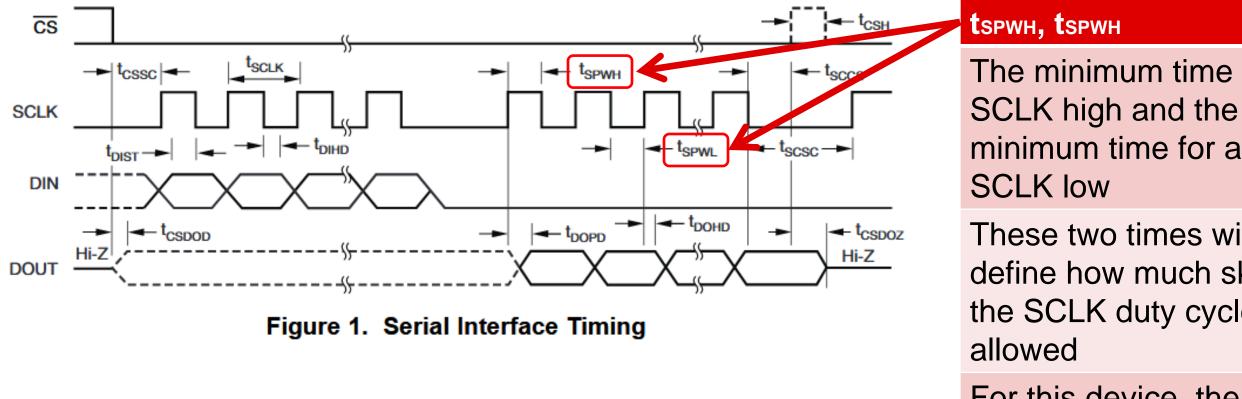

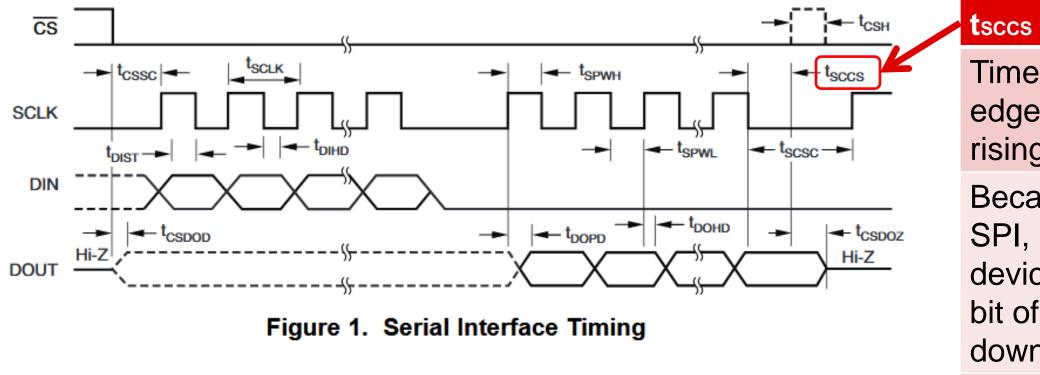

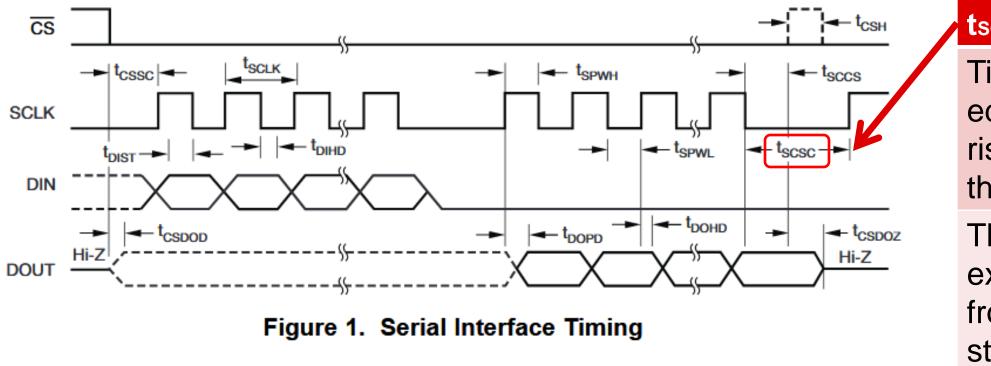

# A timing diagram shows the specifications and the timing relationship between the SPI digital lines

Violating a timing specification can cause a failure to read the data and may cause unexpected results.

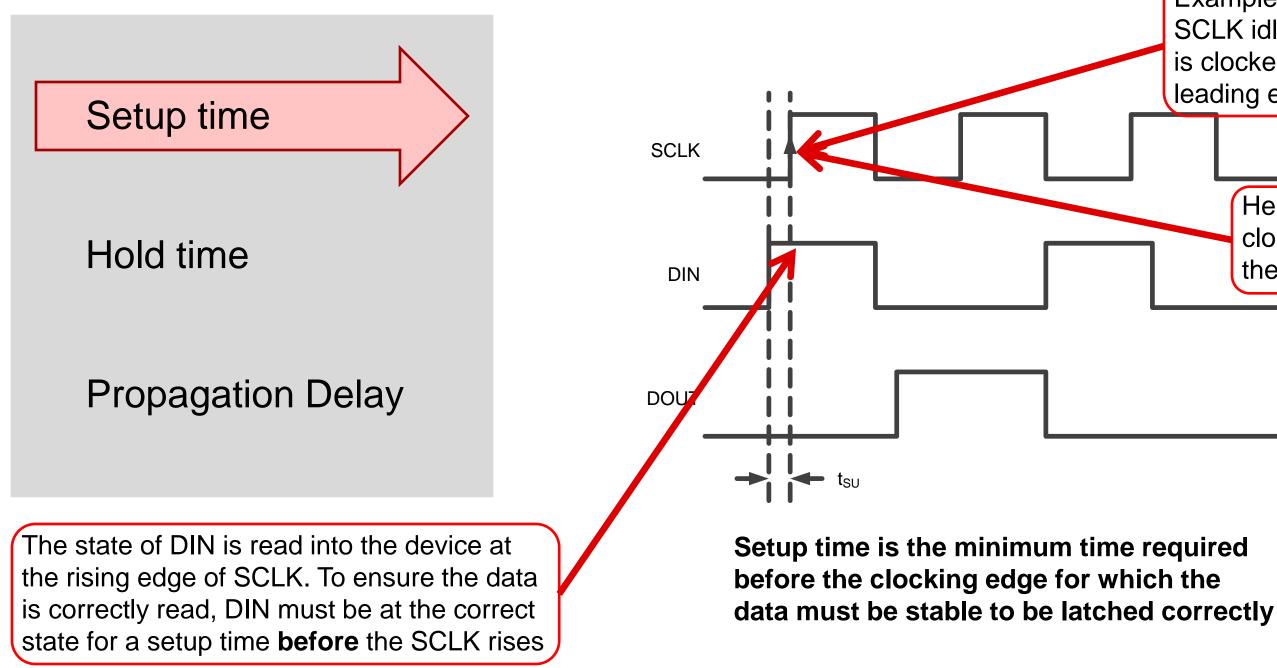

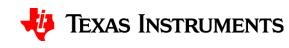

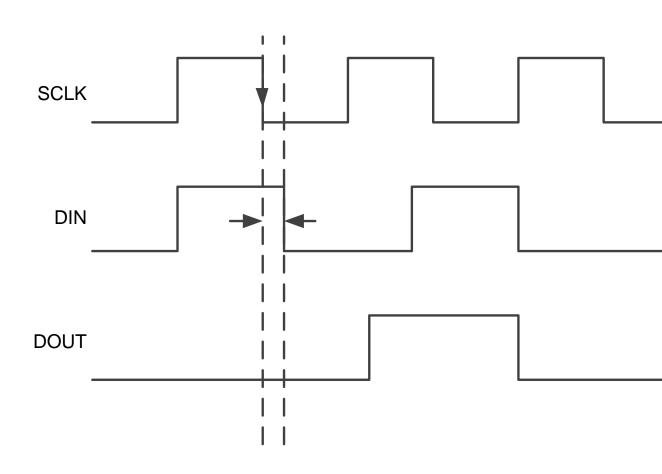

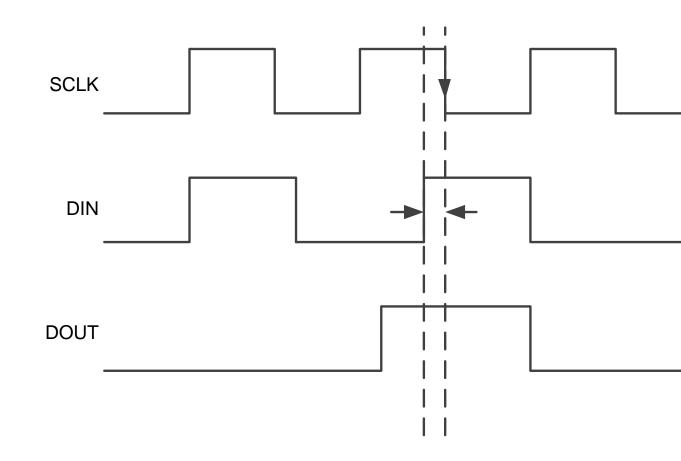

## **SPI Timing: Setup Time**

Example is SPI mode 0: SCLK idles low and data is clocked in on the leading edge of SCLK

> Here, a 1 is clocked into the device

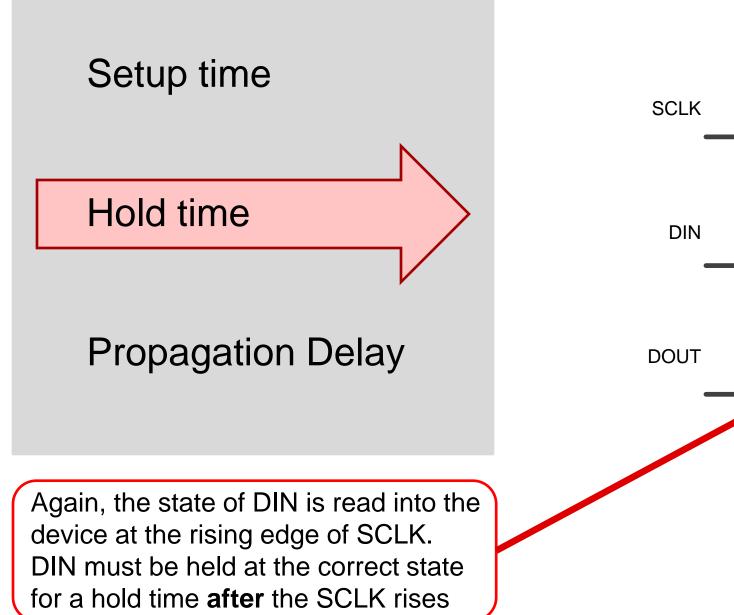

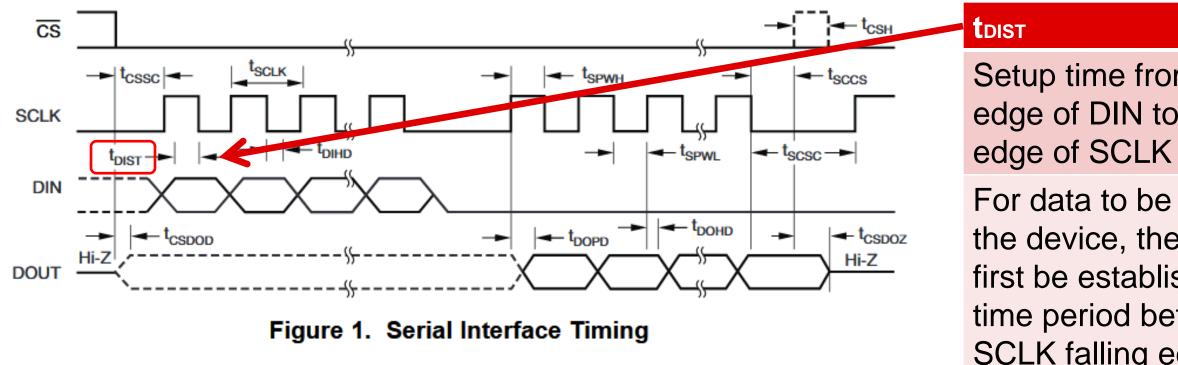

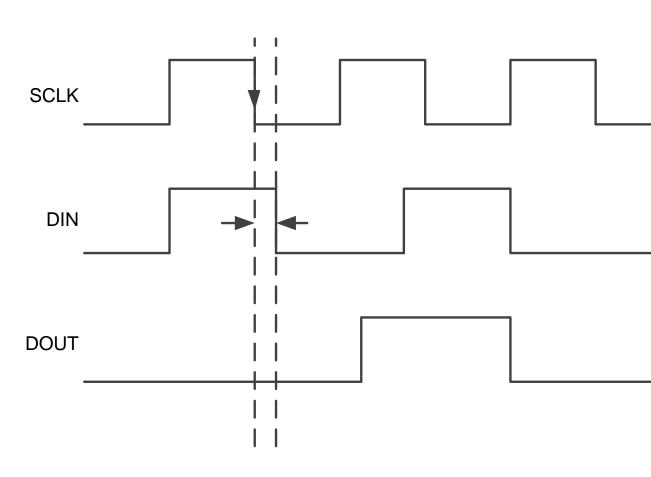

## **SPI Timing: Hold Time**

Hold time is the minimum time required after the clocking edge for which the data must be stable to be latched correctly

4

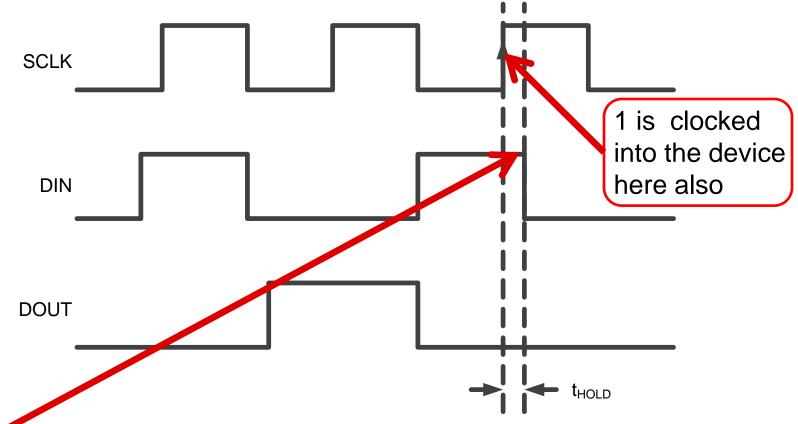

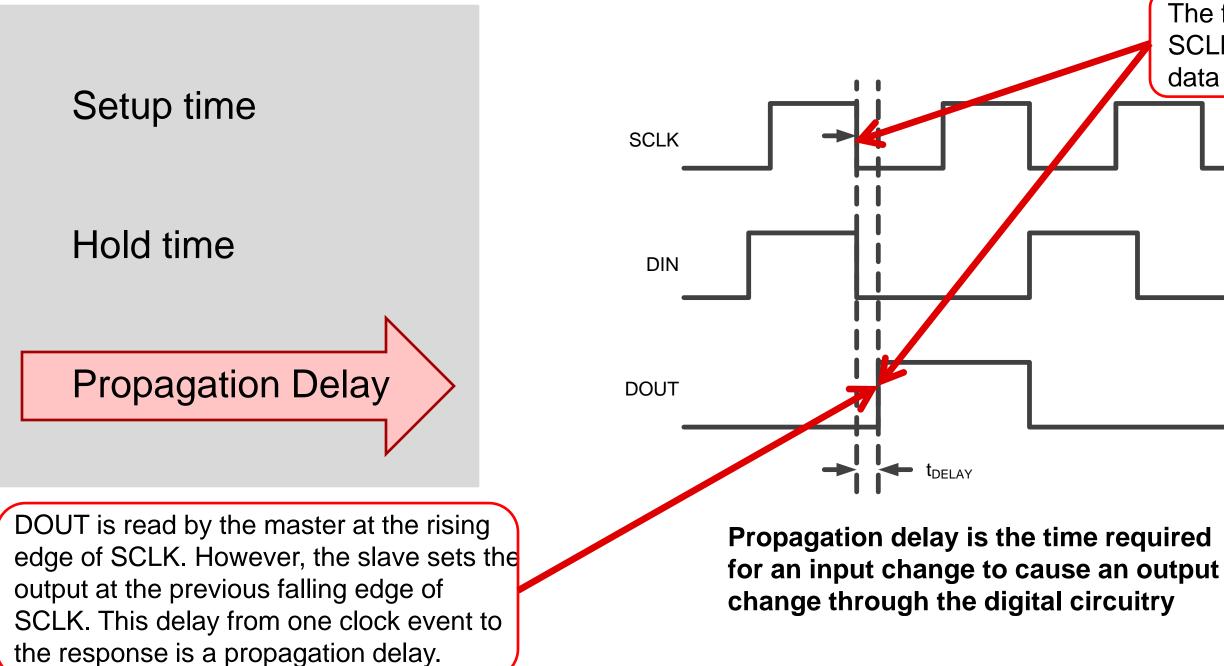

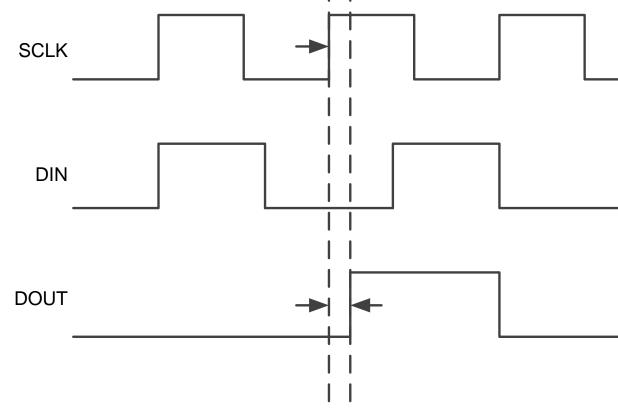

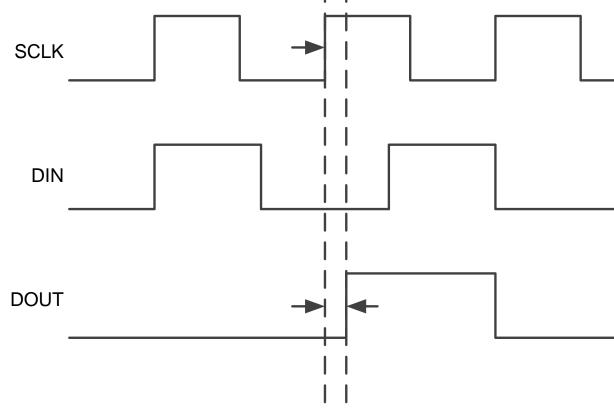

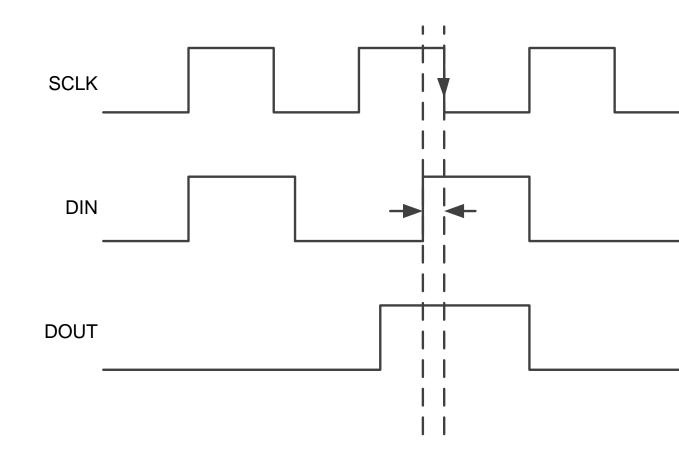

## **SPI Switching: Propagation Delay**

## The falling edge of SCLK sets up the data on DOUT

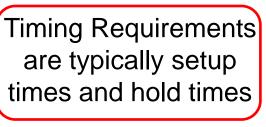

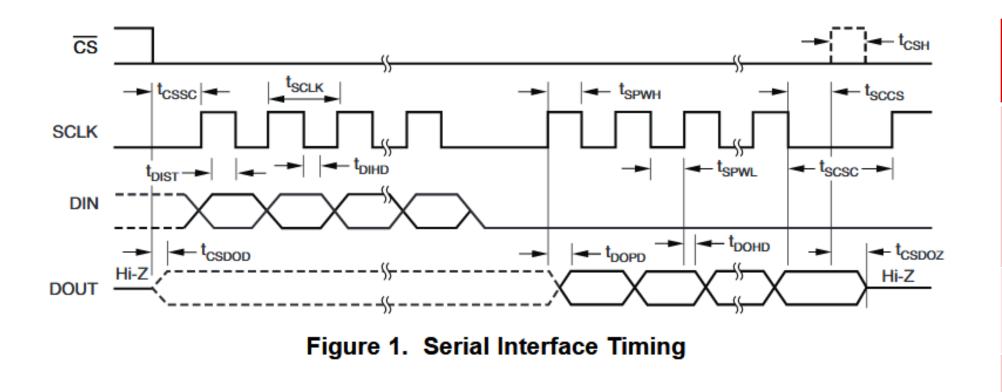

# **SPI** Timing

**Timing Requirements** and Switching **Characteristics** example from the **ADS1118**

## 7.6 Timing Requirements: Serial Interface

Over operating ambient temperature range and VDD = 2 V to 5.5 V (unless otherwise noted)

|                   |                                                                                          | MIN | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------------|-----|-----|------|

| t <sub>CSSC</sub> | Delay time, $\overline{\text{CS}}$ falling edge to first SCLK rising edge <sup>(1)</sup> | 100 |     | ns   |

| tsccs             | Delay time, final SCLK falling edge to CS rising edge                                    | 100 |     | ns   |

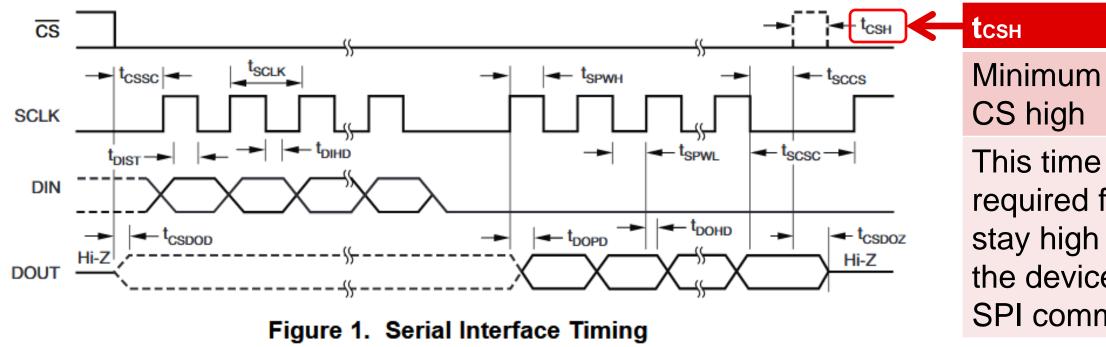

| t <sub>CSH</sub>  | Pulse duration, CS high                                                                  | 200 |     | ns   |

| t <sub>SCLK</sub> | SCLK period                                                                              | 250 |     | ns   |

| t <sub>SPWH</sub> | Pulse duration, SCLK high                                                                | 100 |     | ns   |

| t <sub>SPWL</sub> | Pulse duration, SCLK low <sup>(2)</sup>                                                  | 100 |     | ns   |

|                   |                                                                                          |     | 28  | ms   |

| t <sub>DIST</sub> | Setup time, DIN valid before SCLK falling edge                                           | 50  |     | ns   |

| t <sub>DIHD</sub> | Hold time, DIN valid after SCLK falling edge                                             | 50  |     | ns   |

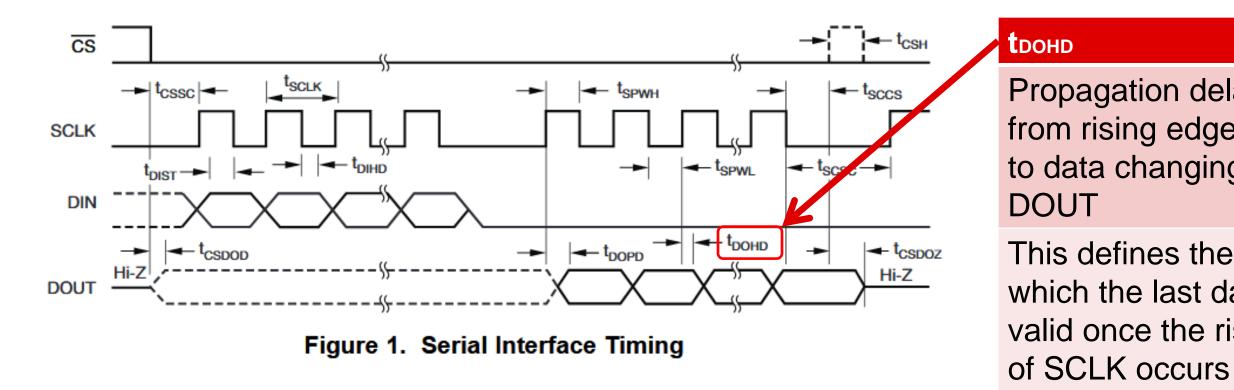

| t <sub>DOHD</sub> | Hold time, SCLK rising edge to DOUT invalid                                              | 0   |     | ns   |

$\overline{CS}$  can be tied low permanently in case the serial bus is not shared with any other device. (1)

Holding SCLK low longer than 28 ms resets the SPI interface. (2)

## **Switching Characteristics** are typically propagation delays

## Switching Characteristics: Serial Interface 7.7

Over operating ambient temperature range (unless otherwise noted)

|                    | PARAMETER                                                        | TEST CONDITIONS                            | MIN | TYP | MAX | UNIT |  |  |  |  |

|--------------------|------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|------|--|--|--|--|

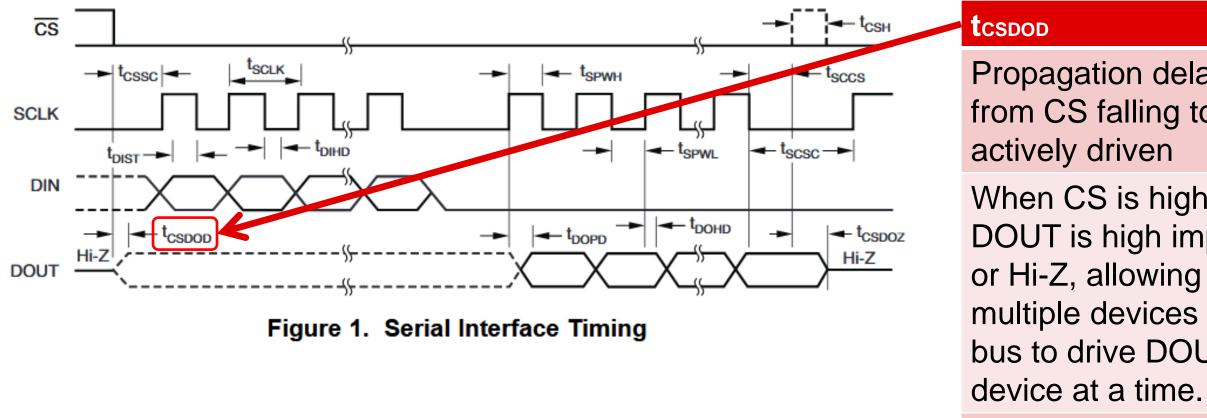

| t <sub>CSDOD</sub> | Propagation delay time,<br>CS falling edge to DOUT driven        | DOUT load = 20 pF    100 k $\Omega$ to GND |     |     | 100 | ns   |  |  |  |  |

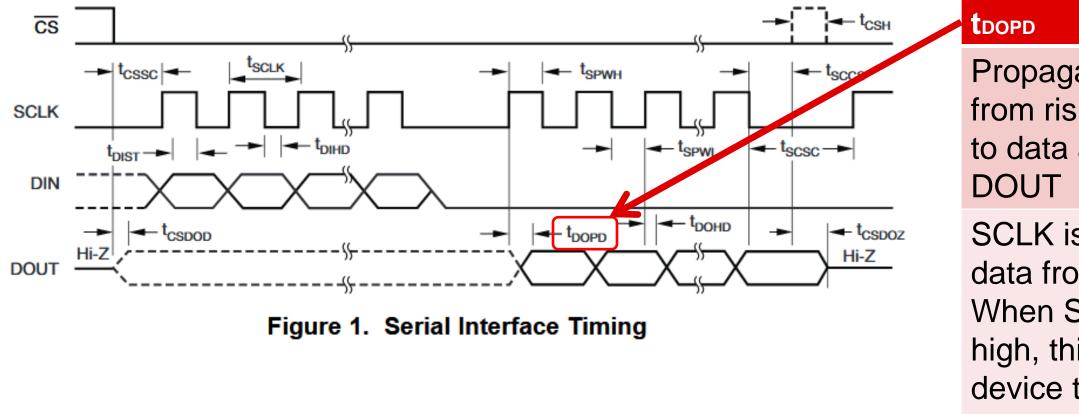

| t <sub>DOPD</sub>  | Propagation delay time,<br>SCLK rising edge to valid new DOUT    | DOUT load = 20 pF    100 k $\Omega$ to GND | 0   |     | 50  | ns   |  |  |  |  |

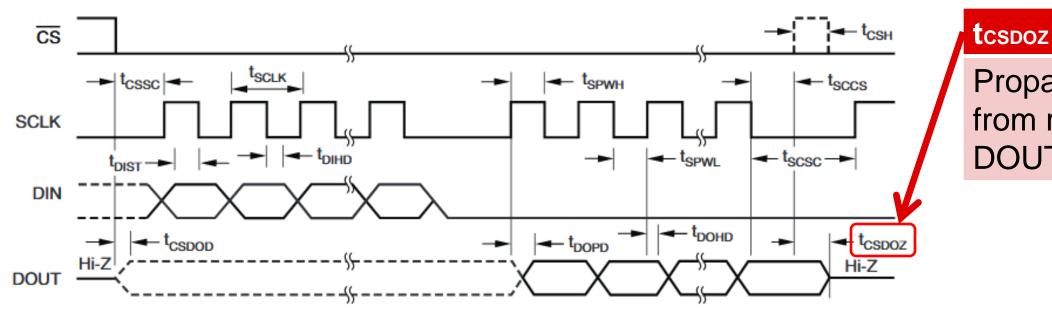

| t <sub>CSDOZ</sub> | Propagation delay time,<br>CS rising edge to DOUT high impedance | DOUT load = 20 pF    100 k $\Omega$ to GND |     |     | 100 | ns   |  |  |  |  |

# **ADS1118**

- of SCLK

- Arrows enclose timing specifications

## Timing diagram for the

Device uses SPI Mode 1: SCLK idles low, data clocked in at falling edge

Boxes for DIN and DOUT are high or low data

## Minimum pulse duration,

This time defines the time required for the CS to stay high to ensure that the device has reset the SPI communications.

SCLK pulse

## CS low to first SCLK high

- This time defines the time required for the CS to stay high to ensure that the device recognizes it

- A violation may cause the device to miss the first

1/tsclk is the SCLK frequency

# The minimum time for an

## SCLKs can be sent to a device only so fast before recognize it. This defines the minimum time for

timeout

The minimum time for an minimum time for an

These two times with tsclk define how much skew in the SCLK duty cycle is

For this device, there is a maximum tspwl for SPI

Time from the falling edge of SCLK to the rising edge of CS Because CS disables the SPI, ensure that the device receives the last bit of data before shutting down SPI communication A violation of this could cause the device to miss the last data transmission

## tscsc

Time from the falling edge of SCLK to the rising edge of SCLK in the next CS

This time is required to execute the command from one CS period, to start a new command in another CS period

Setup time from the rising edge of DIN to the falling

For data to be read into the device, the DIN must first be established for a time period before the SCLK falling edge.

Once the data is set onto the DIN line, the SCLK falling edge latches the data into the device. However, there is a required time for the data to be held after the SCLK falling edge

Hold time from the falling edge of SCLK to the falling edge of DIN.

When CS goes low, DOUT is actively driven

Propagation delay time from CS falling to DOUT

When CS is high, the DOUT is high impedance or Hi-Z, allowing for multiple devices on the bus to drive DOUT a

SCLK is used to clock out data from the device. When SCLK is driven high, this signals to the device that data should be put on DOUT that can be clocked out on the falling edge of DOUT

Propagation delay time from rising edge of SCLK to data appearing on

Propagation delay time from rising edge of SCLK to data changing on

This defines the time for which the last data is still valid once the rising edge

Figure 1. Serial Interface Timing

## Propagation delay time from rising edge of CS to DOUT becoming Hi-Z

# Thanks for your time! Please try the quiz.

20

## © Copyright 2020 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

## Quiz: Basics of SPI: Timing Requirements and Switching Characteristics TIPL xxxx TI Precision Labs – Precision Data Converters

Created by Joseph Wu

- 1. The following diagram is CPOL = 0, CPHA = 1. Data is clocked in on the falling edge of SCLK. DIN must be stable for a time after the SCLK falling edge. This timing is an example of which timing requirement?

- a. Setup time

- Hold time b.

- Propagation delay C.

- d. None of the above

- 1. The following diagram is CPOL = 0, CPHA = 1. Data is clocked in on the falling edge of SCLK. DIN must be stable for a time after the SCLK falling edge. This timing is an example of which timing requirement?

- Setup time a.

- b. Hold time

- Propagation delay C.

- d. None of the above

- 2. The following diagram is CPOL = 0, CPHA = 1. DIN and DOUT are read on the falling edge of SCLK. However, DOUT is set up on the rising edge of SCLK, and there may be time required for the data to arrive on DOUT. This timing is an example of which timing requirement?

- a. Setup time

- Hold time b.

- c. Propagation delay

- d. None of the above

- 2. The following diagram is CPOL = 0, CPHA = 1. DIN and DOUT are read on the falling edge of SCLK. However, DOUT is set up on the rising edge of SCLK, and there may be time required for the data to arrive on DOUT. This timing is an example of which timing requirement?

- a. Setup time

- Hold time b.

- c. Propagation delay

- d. None of the above

26

- 3. The following diagram is CPOL = 0, CPHA = 1. Data is clocked in on the falling edge of SCLK. DIN must be stable for a time before the falling edge of SCLK. This timing is an example of which timing requirement?

- a. Setup time

- Hold time b.

- Propagation delay C.

- d. None of the above

- 3. The following diagram is CPOL = 0, CPHA = 1. Data is clocked in on the falling edge of SCLK. DIN must be stable for a time before the falling edge of SCLK. This timing is an example of which timing requirement?

- a. Setup time

- Hold time b.

- Propagation delay C.

- d. None of the above

# To find more <insert product series name> technical resources and search products, visit ti.com/<insert product portal>